芯片ESD测试全解析:原理、方法、流程与等级标准详解

芯片ESD测试全解析:原理、方法、流程与等级标准详解

静电放电(ESD)是导致芯片早期失效的“头号杀手”,行业数据显示,超过30%的芯片失效都与静电放电相关。无论是芯片研发设计、量产品控,还是终端应用验证,ESD测试都是评估芯片抗静电能力、保障芯片可靠性的核心环节。本文将从原理到落地,全面拆解芯片ESD测试的全流程,为芯片工程师、硬件研发人员提供一份可落地的完整指南。

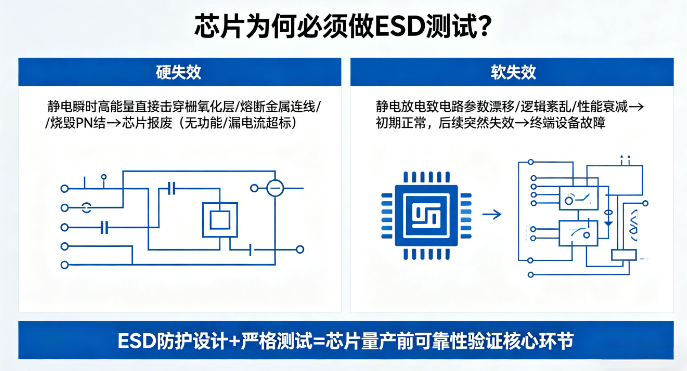

一、为什么芯片必须做ESD测试?

静电放电对芯片的损伤具有隐蔽性和不可逆性,主要分为硬失效和软失效两大类,这也是芯片必须通过严格ESD测试的核心原因:

硬失效:静电瞬时高能量直接击穿芯片栅氧化层、熔断金属连线、烧毁PN结,导致芯片直接报废,外在表现为芯片无功能、漏电流超标、引脚短路,这种损伤不可逆,无法修复。

软失效:静电放电造成芯片电路参数漂移、逻辑紊乱、性能衰减,初期芯片仍可正常工作,但在后续使用中会出现突然失效的情况,极易引发终端设备故障,造成更严重的产品事故。

因此,ESD防护设计和严格的ESD测试,是芯片量产前可靠性验证中不可或缺的核心环节,也是保障芯片全生命周期稳定运行的关键。

二、芯片级ESD测试的三大核心分类

ESD事件可能发生在芯片任意两个引脚之间,且放电应力有正负之分,行业内将芯片级ESD测试分为三大类,覆盖所有可能的 ESD放电场景:

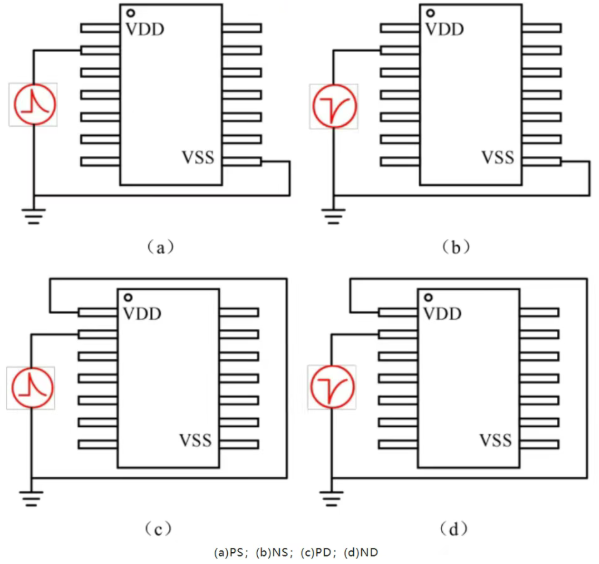

1. I/O引脚对VDD/VSS放电测试

这是芯片ESD测试最基础的项目,针对每个 I/O 引脚(包括输入引脚和输出引脚),需要完成4种组合的放电测试,测试时其他引脚全部浮空,依次对芯片每个 I/O 引脚执行全组合测试。

| 测试组合 | 核心含义 | 放电方式 |

|---|---|---|

| PS | Positive to VSS | 正脉冲对地放电 |

| NS | Negative to VSS | 负脉冲对地放电 |

| PD | Positive to VDD | 正脉冲对电源放电 |

| ND | Negative to VDD | 负脉冲对电源放电 |

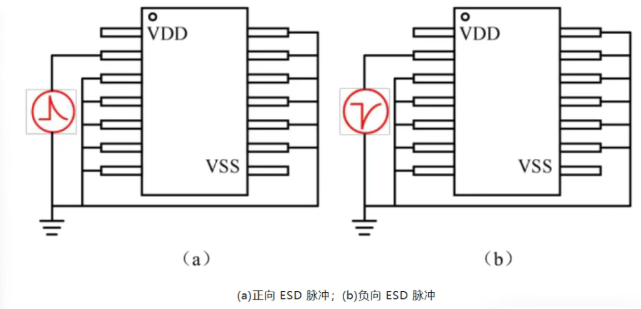

2. I/O 引脚对 I/O 引脚(pin-to-pin)测试

芯片任意两个 I/O 引脚之间都可能形成 ESD 放电回路,若逐一测试所有引脚组合,测试量过大。行业通用测试方法为:在待测 I/O 引脚施加正或负 ESD 脉冲,其他所有 I/O 引脚一起接地,输入输出引脚同时浮空,覆盖引脚间的 ESD 防护能力验证。

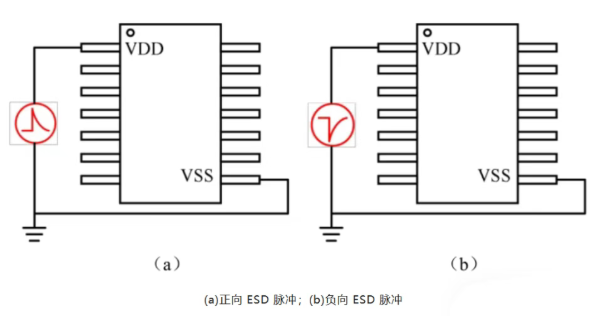

3. VDD 到 VSS 之间放电测试(电源钳位测试)

该测试主要验证芯片电源之间的ESD保护能力(电源钳位性能)。测试方法为:在VDD上施加正负向ESD脉冲,VSS接地,其余 I/O引脚全部悬空;若芯片存在多个电源域,各电源域之间也需要分别完成对应测试。

三、芯片ESD测试主流方法与系统级测试规范

除了核心的芯片级测试,行业内还有通用的系统级ESD测试方法,其中最主流的是IEC系统级测试,主要针对芯片搭载的终端 PCB板、整机系统进行ESD抗干扰能力验证,分为两种测试模式:

接触放电:测试时电子枪口直接对准PCB板、USB口、HDMI接口等待测部位,注入ESD电流,测试过程会产生强烈电磁干扰,是目前系统级ESD测试的主流方式。

空气放电:主要用于难以直接接触的待测部位,通过空气间隙完成 ESD 放电,实际测试中使用频次较低。

四、芯片 ESD 测试标准流程与电压步进规则

芯片 ESD 测试有严格的行业通用流程与电压步进规则,确保测试结果的准确性和可复现性,核心规则如下:

基础放电规则:在每个测试模式下,同一测试电压需要连续放电(Zap)3 次,每次放电间隔约 1 秒;极端严苛测试场景下,可提升至 5 次放电。若芯片未出现损坏,则调高电压继续测试,直到找到芯片损坏临界值,该数值即为芯片 ESD 故障临界电压。

起始电压设定:测试起始电压一般设定为芯片平均故障临界电压的 70%,例如某芯片 HBM 耐压平均值约 2000V,则测试起始电压为 1400V。

电压步进规则:行业通用电压步进经验法则如下,可根据芯片测试需求调整步进幅度。

| 测试电压范围 | 每次电压增量标准 |

|---|---|

| <1000V | 50V 或 100V |

| ≥1000V | 100V、250V 或 500V |

五、芯片 ESD 损坏的三大核心判定方法

完成 ESD 测试后,行业内有三种通用的芯片失效判定方法,不同判定准则会得出不同的故障临界电压,因此出具 ESD 测试报告时,必须明确标注对应的判定方法。

绝对漏电流法:ESD 测试后,I/O 引脚漏电流超过 1μA 或 10μA(测试偏压常用 5.5V 或 7V),即可判定芯片 ESD 失效。

相对 I-V 漂移法:ESD 测试后,芯片 I-V 特性曲线漂移超过 30%(行业通用标准,也可根据产品需求调整为 20%/40%),即可判定芯片 ESD 失效。

功能观测法:完成 ESD 脉冲注入后,全面测试芯片各项功能,验证是否仍符合产品规格书要求,若出现功能异常,即可判定芯片 ESD 失效。

六、芯片 ESD 测试行业等级典型指标

芯片 ESD 测试有三大核心模型,不同模型对应不同的行业防护等级标准,商用集成电路、功率芯片、车规芯片的等级要求差异显著,行业典型指标如下:

| 测试模型 | 行业典型防护等级 | 核心备注 |

|---|---|---|

| HBM(人体放电模型) | 消费电子 2kV,车规级可达 8kV | 商用集成电路基础标准 2kV,功率芯片要求≥4kV,高压芯片可达 8kV |

| MM(机器放电模型) | 200V~800V | 通常为 HBM 防护等级的 1/10,商用集成电路基础标准 200V |

| CDM(器件放电模型) | 500V,峰值电流 20A | 商用集成电路通用标准 500V,是芯片量产测试的必测项目 |

七、芯片 ESD 测试的质量管理核心要点

芯片 ESD 防护不是单只芯片、单个引脚的性能问题,而是整批芯片的量产可靠性问题,测试过程中的质量管理核心要点如下:

取样规则:同一批芯片中,随机取样至少 5 颗以上完成全项 ESD 测试,取样数量越多,测试结果越精准。

临界值判定:每颗芯片单独测试得出 ESD 故障临界电压,取其中最低值,作为该批次芯片的 ESD 故障临界电压。

全场景覆盖:测试过程中必须覆盖所有 ESD 放电场景,充分验证不同放电情况下,电流在芯片内部的流动路径与防护能力,避免出现测试盲区。

结语

ESD 测试是芯片可靠性验证中不可或缺的核心环节,从 I/O 引脚对电源地的基础测试、pin-to-pin 引脚间测试,到电源钳位测试,从芯片级模型测试到系统级 IEC 测试,每一个测试环节,都直接决定着芯片在实际应用中的 “抗静电生存能力”。

只有在芯片设计之初做好 ESD 防护设计,在量产阶段完成严格的 ESD 测试验证,才能真正为芯片穿上 “防静电铠甲”,大幅降低芯片早期失效风险,保障产品全生命周期的稳定运行。

热门资讯

最新资讯

- 芯片ESD测试全解析:原理、方法、流程与等级标准详解

- 芯片失效分析实战指南:精准定位失效根源,护航国产芯片良率提升

- 收藏 | 史上最全失效分析指南:PCB、金属、高分子检测方法汇总

- PCB切片分析:揭秘电路板内部质量的利器

- 塑料产品CT扫描:工业无损检测的革命性技术

- 工业CT三维重建技术全解析:从断层扫描到高精度3D模型的内部透视逻辑

- PCBA失效分析怎么做?第三方机构详解7步标准流程

- 工业CT缺陷检测:气孔裂纹夹杂一次看清

- PCBA失效分析 | 二极管焊点疲劳开裂案例拆解

- 工业CT扫描多少钱一次?深度解析2026年检测费用标准与影响因素

- 工业CT无损检测原理详解:从X射线到三维重建

- 工业CT无损检测费用公开:按小时还是按件?岛津225KV设备实测,这样计费更划算!

- 热重分析测试怎么做才准?TGA Q500实测案例告诉你答案

- 贴片电容失效分析:3大常见击穿原因及真实案例解读

- 工业CT检测在制造业中的应用

- TGA热重分析测试:材料热稳定性与成分分析指南

- 工业CT检测如何提高产品质量?一个真实案例告诉你答案

- 芯片BGA不良失效分析:从焊点开裂到识别不到设备的全面解析

- 工业CT扫描在逆向三维建模中的高精度应用

- 从工业CT到三维分析:工业CT无损检测如何赋能产品研发与失效分析?